ISSN: 0974-2115 Journal of Chemical and Pharmaceutical Sciences

# Consistent endeavor for self-control voltage Based undulate transmit addition

V. Srinivasan\*, M. Sundararajan

Department of ECE, Bharath University, Chennai.

\*Corresponding author: E-Mail: srinivasan.etc@bharathuniv.ac.in

#### ABSTRACT

Presently days, power dispersal is a standout amongst the most imperative issues in advanced circuit outline. CMOS based double mode rationale (DML) has as of now been actualized which accomplishes similarly low power scattering, deferral, zone and number of transistor in the legitimate way contained CMOS-Based DML rationale entryways and through the conservative yields. In this paper a poise voltage (SCV) strategy is presented for further decreasing the force dissemination, postponement, region and number of transistor in the legitimate ways and produce the effective yields contrasted and CMOS-Based DML rationale doors utilizing two controller are class An and class B to control the whole circuits. The proposed SCV rationale is actualized in outlining a swell convey viper to give proficient results and the yield proportion is 90% utilizing standard 130-nm innovation.

KEY WORDS: Reduced Area, Delay, Low Power, Ripple Carry Adder, Self-Control Voltage.

### **1. INTRODUCTION**

The advanced circuits plan expends more power, territory and has expanded postponement. The double mode rationale (DML) door defeat this issue utilizing two methods of operation is 1) static and 2) dynamic mode. In static mode low power dispersal and elite in element mode contrasted and standard CMOS door. The DML rationale is utilized to beat the deferral advancement, delay estimation and way length minimization in the legitimate ways. A fundamental DML entryway is made out of any static rationale family doors and an extra timed transistor. The DML rationale gives abnormal state adaptability to the fashioner and permits the operation exchanging between this two modes on-the-fly.

This consistent exertion (LE) system is additionally utilized as a part of the estimation of measure of rationale stages in the way furthermore utilized as a part of deciding the best transistor sizes to be utilized as a part of the rationale entryways. In the LE system is utilized to plan the computerized circuit for acquiring rationale improvement and timing estimation process in the legitimate way contained standard CMOS door. The bound together coherent exertion (ULE) strategy is utilized to defer assessment and streamlining the rationale ways in the DML rationale.

In DML rationale doors the force dispersal is expanded because of consistent voltage scaling guidelines connected. Keeping in mind the end goal to maintain a strategic distance from these issues the new strategy is presented called Self-control voltage (SCV). The SCV fabricated with two controllers for draw up system and draw down system. The PMOS transistor will go about as a draw up system and NMOS transistor will go about as a draw up system in the SCV-based DML rationale.

The point of this paper is to propose a straightforward strategy for minimizing defer and accomplishing advanced number of stages utilizing this SCV method. In this SCV will diminish the most extreme number of force dissemination, deferral, range and number of transistor in the SCV-Based DML rationale doors. The computerized circuit are anything but difficult to recreate and plan to the creator utilizing this SCV method as a part of the sensible way. In this paper to execute a swell convey snake (RCA) utilizing SCV technique. Here the base number of transistors is utilized to actualize this RCA configuration. The target of this paper is to add to a straightforward strategy for minimizing deferrals, accomplishing an advanced number of stages and diminished the force dispersal in intelligent way containing SCV-based RCA.

**Literature Review:** In the work talked about the DML rationale family works in the sub edge area. Here two modes, static and element modes are worked in DML topologies sort an and sort B. The PMOS transistor are joined with the sort A topology with the legitimate yield "1" to the pre-charge stage and NMOS transistor are associated with the sort B topology with the intelligent yield "0" to the pre-charge stage. Here low power dispersal in static mode and superior in element mode are accomplished. It is actualized with the assistance of 80-nm processor. Bound together consistent exertion (ULE) is utilized as a part of deferral assessment and minimization in legitimate way. The postponement minimization is most imperative subject considered in the incorporated circuits with high unpredictability plan. The deferral model utilized as a part of this outline incorporates different postpones, for example, the interconnect deferral, wire delay and the door LE delay. At the point when these postponements are incorporated into the LE model it gets to be ULE model. Here the 65-nm processors are utilized to actualize this procedure to the legitimate way.

Convey look ahead snake is actualized utilizing double mode rationale (DML). This DML rationale permits the CLA operation to be powerfully picked furthermore exchanged in the middle of static and element methods of operation. The DML topology is utilized as a part of footed and un-footed arrangement. Here the DML footed door

#### Journal of Chemical and Pharmaceutical Sciences

introduces the zero short out force amid pre-charge and short pre-charge stage to the CLA execution to get the elite contrasted and CMOS CLA operation. Procedure is executed in 40-nm processor. Domino circuits are utilized to give superior contrasted with CMOS microchip in the work.

Domino circuits portray a deliberate edge work called skew –tolerant to covering the timekeepers. Domino circuits are progressively well known in light of the fact that they offer a huge execution support over static entryways. The course book domino timing systems on high-recurrence chips lose quite a bit of their advantage to timing overhead. Creators have understood that covering domino timekeepers can be utilized to ensure that information swells through domino entryways when it arrives, regardless of the fact that tickers are skewed. Wiping out locks decreases the inertness of the basic way and permits time obtaining.

The adjusted consistent exertion procedure is utilized to give the postponement estimation to CMOS entryways and the conduct of arrangement joined MOSFET structure. This model shows great precision to contrast and ghost reenactment in view of BSIM3v3 model. This model is composed utilizing 0.18-m advances. Creators are required to gauge the single ways and enhance the same by demonstrating equally the proliferation and move time. Sensible exertion strategy is for the most part utilized method for accomplishing the above displaying. This model is executed on 130-nm STMicroelectronics innovation.

A general and finish outline philosophy for nanometer FFs are proposed, prompting a measuring methodology for every transistor inside of the circuit and to diminish the extent of the configuration space by utilizing 65-nm innovation. The CMOS-Based double mode rationale (DML) family was proposed to work in two modes 1) static and 2) dynamic mode. It permits the operation in these two modes on-the-fly. The static mode accomplishes low power dispersal and superior is accomplished in element mode. Here the sort an and sort "B" two topologies are utilized. The sort a topology is associated with draw up system and sort "B" topology is joined with draw down system. The draw up system and draw down system utilize absolute

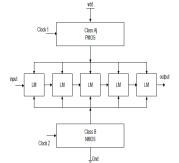

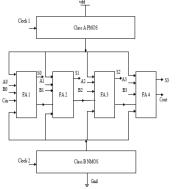

**Proposed System:** The SCV chip power dispersal has kept on expanding subsequent to turning into a standard innovation. At the point when consistent voltage scaling standards were connected, the force dissemination expanded in double mode rationale (DML). The framework proposed in this paper utilizes the SCV innovation for decreasing force scattering, region and postponement in the rationale way contained SCV-Based DML rationale. SCV strategy presents two controller which are draw up system Class an and draw down system Class B are appeared in the figure.1.

These two controllers always keep up the information, yield information and check information in the SCVbased DML rationale doors. Legitimate exertion (LE) system has turned into an exceptionally well known device for outlining and instruction purposes and is embraced to be the premise for a few PC helped configuration apparatuses. The target of this paper is to build up a basic strategy for minimizing deferrals, accomplishing an upgraded number of stages and diminish the force dispersal in coherent way containing SCV-based DML entryway.

This DML rationale conquers the postponement advancement, delay estimation and way length minimization, in the standard CMOS-based DML rationale. The static and element modes are utilized to sort a topology and sort B topology on-the-fly. The DML door accomplishes low power dissemination in static mode and elite in element mode contrasted with standard CMOS entryway. Here the worldwide clock sign is connected to the class an and class B systems.

The class a system are joined with the VDD terminal to give the supply voltage to the DML rationale circuit and the class B system are associated with the ground terminal. In rationale modes are associated with arrangement in the CMOS DML mode and all rationale modes are "ON" condition in the meantime and rationale mode gets the data from past stage yield and it stays in ON condition until information is accessible from the past stage.

The check is empowered in the dynamic mode to permit the operation in two separate stages: 1) pre-charge and 2) assessment. In the pre-charge stage, the yield is charged to VDD through sort an entryways and released to GND through sort B doors. The yield is assessed with the estimations of door information. The static operation of the DML doors is utilized to essentially decrease vitality utilization to the detriment of 2–4 times lessening in execution.

In this SCV technique are utilized to DML rationale circuit are appeared in the figure.1. The SCV-Based DML door is appeared in the figure 1, lessening in force scattering, region and deferral results are appeared in examination table 1 and the yields are talked about in area. In this SCV procedure are utilized to execute the swell convey viper and the yield waveform are appeared in segmen

Figure.1. Block Diagram for SCV-Based DML Logic Gates.

# Working Principle:

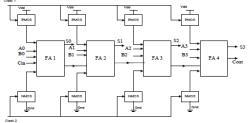

**CMOS and SCV-Based Ripple Carry Adder:** It is conceivable to make a coherent circuit utilizing various full adders to include N-bit numbers and every full snake inputs a Cin given from past viper Cout. This kind of snake is known as a swell convey viper, since every convey bit "swells" to the following full viper. Note that the first (and just the first) full snake may be supplanted by a half viper (under the supposition that Cin = 0).

The format of a swell convey viper is basic utilizing MICRO-WIND, which takes into account quick plan time to the planner. Since every full viper must sit tight for the convey bit to be figured from the past full snake in the CMOS-Based RCA. The entryway postponement can undoubtedly be computed by examination of the full snake circuit.

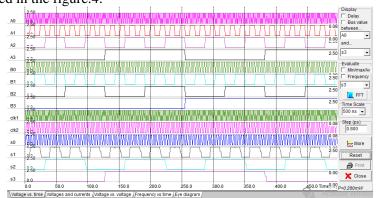

Here the CMOS-Based Ripple Carry Adder Diagram is appeared in the figure.2. In this CMOS-Based Ripple Carry Adder are utilized to 8-transistor joined with draw up system and draw down system and its give the conservative yields are appeared in the figure.4. In this RCA configuration are actualized utilizing the smaller scale wind and computerized schematic circuit (DSCH). These instruments are effectively to outlining the procedure.

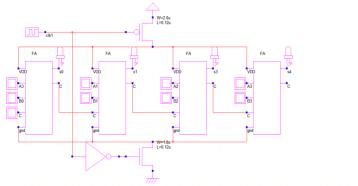

In this SCV-Based swell convey snake (RCA) square graph are appeared in the figure.5. Here the full viper circuits are joined into the arrangement association. The consequence of this swell convey viper is appeared in the table 1 and the yields are productive contrasted and the CMOS-Based Ripple Carry Adder. Here the worldwide clock signs are created to the data signal for class An and class B innovation. The full snake is joined with arrangement

# Figure.2. Block Diagram for CMOS-Based Ripple

Fig. 2: Block Diagram for CMOS-Based Ripple Carry Adder association with produce the yield starting with one stage then onto the next stage and the yields are measured utilizing this HDL apparatuses. The yields are computed from a0 to s4 are appeared in segment. In this SCV system will decrease the greatest force scattering, region, postpone and number of transistor into the RCA circuit.

# Usage of CMOS and SCV-Based Ripple Carry Adder

**CMOS-Based Ripple Carry Adder:** The CMOS-Based Ripple Carry Adder (RCA) schematic graph is appeared in the figure.2. The design of this CMOS-Based RCA circuit is appeared in the figure.2. Here the yields are ascertained from A0 to S3 and the yield waveforms are appeared in the figure.4.

Figure.3. Layout Design for CMOS-Based Ripple Carry Adder. July - September 2016

Figure.4. Output Waveform for CMOS-Based Ripple Carry Adder S -217 JCPS Volume 9 Issue 3

#### Journal of Chemical and Pharmaceutical Sciences

**SCV-Based Ripple Carry Adder:** The SCV-Based RCA will deliver the two controllers for draw up and draw down system to always keep up the information, yield information and clock information to the RCA circuit. The schematic outline for SCV-Based RCA are Shown in the figure.6 and design of this schematic are appeared in figure .7 at long last the yield of this SCV-Based RCA circuit are appeared in the figure.8.

This RCA usage are utilized to this SCV approach to control the whole circuit and it's created this outline utilizing standard 130-nm innovation utilizing miniaturized scale wind devices and give the productive yields. Here the yields are computed from A0 to S3 and the yield proportion is 90% contrasted and CMOS-Based swell Carry Adder Circuits

Figure.5. Block Diagram for SCV-Based Ripple Carry Adder.

### Figure.7. Layout Design for SCV-Based Ripple Carry Adder.

Figure.6. Schematic Diagram for SCV-Based Ripple Carry Adder.

| A0<br>A1 | 250<br>250<br>250                                                                              |                                          |                |                     |                      | A0 +                                |  |  |

|----------|------------------------------------------------------------------------------------------------|------------------------------------------|----------------|---------------------|----------------------|-------------------------------------|--|--|

|          | 2.50                                                                                           |                                          |                |                     | 2.50                 | s3 •                                |  |  |

| A3<br>B0 | 2.5q<br>.3.6g                                                                                  |                                          |                |                     | 2.55                 | Evaluate<br>Min/max/Av<br>Frequency |  |  |

| B1       | 250                                                                                            |                                          |                |                     |                      | 83 •                                |  |  |

| B2       | 2.50                                                                                           |                                          |                |                     | 2.50                 | Time Scale                          |  |  |

|          | 2.80                                                                                           |                                          |                |                     | 2.50                 | 500 ns •                            |  |  |

| dk1      | 26                                                                                             |                                          |                |                     |                      | Step (ps)<br>0.800                  |  |  |

| s0       | i i i i i i i i i i i i i i i i i i i                                                          | a an | NAMANAN MANANA | A. ALAMAN AND AND A |                      | More N                              |  |  |

|          | 250 M. M.                                                                                      | a Mar Mar Mar                            |                |                     |                      | Reset                               |  |  |

|          | 280                                                                                            |                                          |                |                     |                      | Print                               |  |  |

|          | 0.0                                                                                            |                                          |                |                     | 0.35                 |                                     |  |  |

|          | 0.0 50.0                                                                                       | 100.0 150.0                              | 200.0 250.0    | 300.0 350.0         | 400.0 450.0 Time, 35 | P=0.254mW                           |  |  |

| Voltage  | Voltage vs. time /Voltages and currents /Voltage vs. voltage /Frequency vs.time /Eye diagram / |                                          |                |                     |                      |                                     |  |  |

Figure.8. Output Waveform for SCV-Based Ripple Carry Adder

#### 2. RESULT DISCUSSION

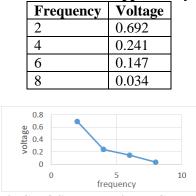

In this segment, the proposed framework results have been talked about. The correlation table for CMOS and SCV-Based Ripple Carry Adder yields are appeared in the table 1. This SCV procedure will used to decrease the most extreme force dispersal, territory, postpone and number of transistor are accomplished in this rationale. The proposed framework will demonstrated the productive yields contrasted and the CMOS-Based Ripple Carry Adder.

| Table.1. Comparison for CiviOS & SCV-based Ripple Carry Adder |                 |                 |                     |  |  |  |  |  |

|---------------------------------------------------------------|-----------------|-----------------|---------------------|--|--|--|--|--|

| Parameters                                                    | Existing system | Proposed system | obtained percentage |  |  |  |  |  |

| Power dissipation                                             | 0.280 mW        | 0.254 mW        | 9%                  |  |  |  |  |  |

| Area                                                          | 20690.4µm       | 16533.6µm       | 41%                 |  |  |  |  |  |

| Delay                                                         | 512ns           | 112ns           | 40%                 |  |  |  |  |  |

| Number of                                                     | 8               | 2               | 40%                 |  |  |  |  |  |

| transistors                                                   |                 |                 |                     |  |  |  |  |  |

Table.2. CMOS-Based Ripple Carry Adder

Figure.9. CMOS-Based Ripple Carry Adder S -218

#### ISSN: 0974-2115

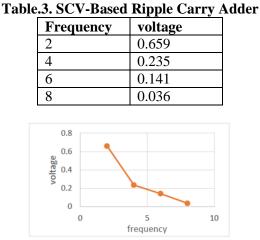

Recurrence reaction of the CMOS and SCV-Based swell convey snake as for voltage is appeared in the Fig 9 and 10.

#### **3. CONCLUSION**

An inventive legitimate exertion (LE) approach for SCV-Based Ripple Carry Adder was exhibited. The proposed methodology permitted a proficient force utilization of Ripple Carry Adder, which is the center of this paper. This paper presents SCV system to lessen the force scattering, territory, postpone and number of transistor. In this SCV strategy will present two controllers for draw up and draw down system to continually keep up the clock information, data information and yield information. This strategy will give the financial yield proportion of 90% and the reenactment results appeared in 130-nm process.

#### REFERENCE

Alioto M, Consoli E and Palumbo G, General strategies to design nanometer flip-flops in the energy-delay space, IEEE Trans. Circuits Syst. I, Regular Papers, 57(7), 2010, 1583–1596.

Al-Khalili A.J, Al-Khalili D and Kabbani A, Delay analysis of CMOS gates using modified logical effort model, IEEE Trans. Com- put. Aided Design Integr. Circuits Syst, 24(6), 2005, 937–947.

Auvergne D, Azemard N, Engels S, Maurine P, Lasbouygues B and Wilson R, Logical effort model extension to propagation delay representation, IEEE Trans, Comput. Aided Design Integr, Circuits Syst, 25(9), 2006, 1677–1684.

Bass O, Belenky A, Fish A, Levi I and Kaizerman A, High speed dual mode logic carry look ahead adder, in Proc. IEEE Int Symp Circuits Syst, 2012, 3037–3040.

Belenky A, Fish A, Levi I, logical effort for CMOS-based dual mode logic gates, IEEE Trans Very Large Scale Integr (VLSI) Syst, 22(5), 2014.

Chiueh H, Lin S.H and Wu C.H, Logical effort model extension with temperature and voltage variations, in Proc 14th Int Workshop Thermal Invest ICs Syst, THERMINIC, 2008, 85-88.

Fish A, Fisher S and Kaizerman A, Subthreshold dual mode logic, IEEE Trans. Very Large Scale Integr. (VLSI) Syst, 21(5), 2013, 979–983.

Fish A, Kaizerman A and Levi I, Low voltage dual mode logic, Model analysis and parameter extraction, Excepted Elsevier, Microelec-tron J, 12(1), 2012

Friedman E.G, Ginosar R, Kolodny A and Morgenshtein A, Cor- rections to unified logical effort-a method for delay evaluation and minimization in logic paths with RC interconnect, IEEE Trans, Very Large Scale Integr. (VLSI) Syst, 18(8), 2010, 689–696.

Gopalakrishnan K, Sundar Raj M, Saravanan T, Multilevel inverter topologies for high-power applications, Middle - East Journal of Scientific Research, 20(12), 2014, 1950-1956.

Harris D and Horowitz M.A, Skew-tolerant domino circuits, IEEE J. Solid-State Circuits, 32(11), 1997, 1702–1711.

Jasmin M, Vigneshwaran T, Beulah Hemalatha S, Design of power aware on chip embedded memory based FSM encoding in FPGA, International Journal of Applied Engineering Research, 10(2), 2015, 4487-4496.

# Journal of Chemical and Pharmaceutical Sciences

Kanniga E, Selvaramarathnam K, Sundararajan M, Kandigital bike operating system, Middle - East Journal of Scientific Research, 20(6), 2014, 685-688.

Kanniga E, Sundararajan M, Modelling and characterization of DCO using pass transistors, Lecture Notes in Electrical Engineering, 86(1), 2011, 451-457.

Karthik B, Arulselvi, Noise removal using mixtures of projected gaussian scale mixtures, Middle - East Journal of Scientific Research, 20(12), 2014, 2335-2340.

Karthik B, Arulselvi, Selvaraj A, Test data compression architecture for low power vlsi testing, Middle - East Journal of Scientific Research, 20(12), 2014, 2331-2334.

Karthik B, Kiran Kumar T.V.U, Authentication verification and remote digital signing based on embedded arm (LPC2378) platform, Middle - East Journal of Scientific Research, 20(12), 2014, 2341-2345.

Karthik B, Kiran Kumar T.V.U, EMI developed test methodologies for short duration noises, Indian Journal of Science and Technology, 6(5), 2013, 4615-4619.

Karthik B, Kiran Kumar T.V.U, Vijayaragavan P, Bharath Kumaran E, Design of a digital PLL using 0.35Î<sup>1</sup>/4m CMOS technology, Middle - East Journal of Scientific Research, 18(12), 2013, 1803-1806.

Philomina S, Karthik B, Wi-Fi energy meter implementation using embedded linux in ARM 9, Middle - East Journal of Scientific Research, 20(12), 2014, 2434-2438.

Saravanan T, Sundar Raj M, Gopalakrishnan K, Comparative performance evaluation of some fuzzy and classical edge operators, Middle - East Journal of Scientific Research, 20(12), 2014, 2633-2633.

Saravanan T, Sundar Raj M, Gopalakrishnan K, SMES technology, SMES and facts system, applications, advantages and technical limitations, Middle - East Journal of Scientific Research, 20(11), 2014, 1353-1358.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, A DFIG based wind generation system with unbalanced stator and grid condition, Middle - East Journal of Scientific Research, 20(8), 2014, 913-917.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, Effective routing technique based on decision logic for open faults in fpgas interconnects, Middle - East Journal of Scientific Research, 20(7), 2014, 808-811.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, Privacy conscious screening framework for frequently moving objects, Middle - East Journal of Scientific Research, 20(8), 2014, 1000-1005.